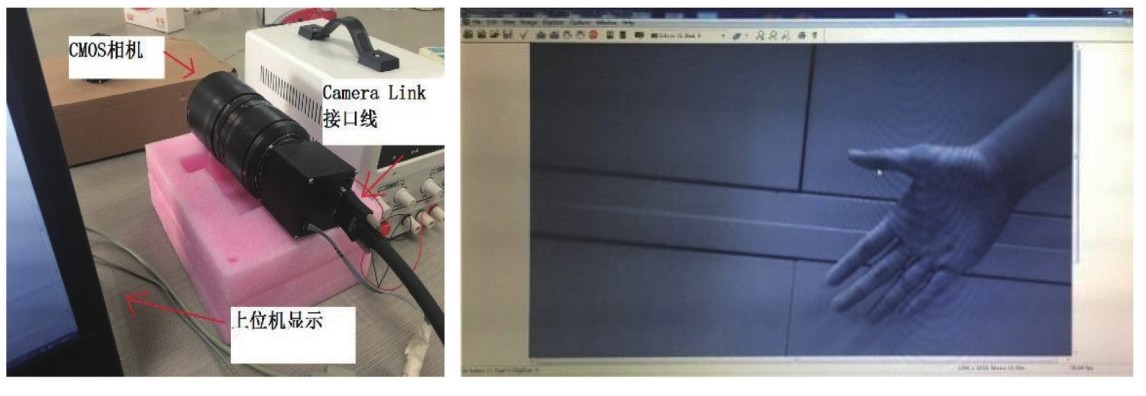

Camera Link协议是基于低压差分信号(LVDS)形式传输的,通过一对差分PCB走线或平衡电缆传输数据。Camera Link信号包括图像数据信号、相机控制、串行通信信号和电源信号。其中图像数据包括28个单端数据信号和1个时钟信号。一般使用的并串转换芯片为TI公司的DS90CR287。该芯片将这些信号以7:1的比例串行发送,输出4对LVDS数据流和1对LVDS时钟信号。在FPGA内部编码并串转换模块来实现Camera Link协议,实现的功能与DS90CR287相同。在完成数据的并串转换的功能后,通过FPGA的LVDS差分管脚直接对外输出。

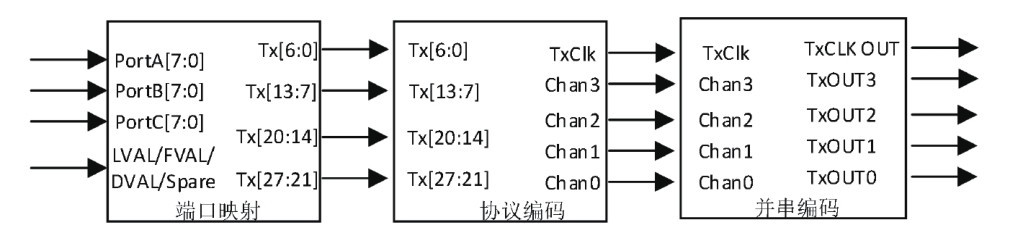

并串转换模块主要分为3个部分:端口映射、协议编码、并串编码。信号流程如图4所示。

图4 Camera Link并串转换模块信号流程图Fig.4 Camera Link parallel-serial conversion module signal flow chart

2.1 端口映射

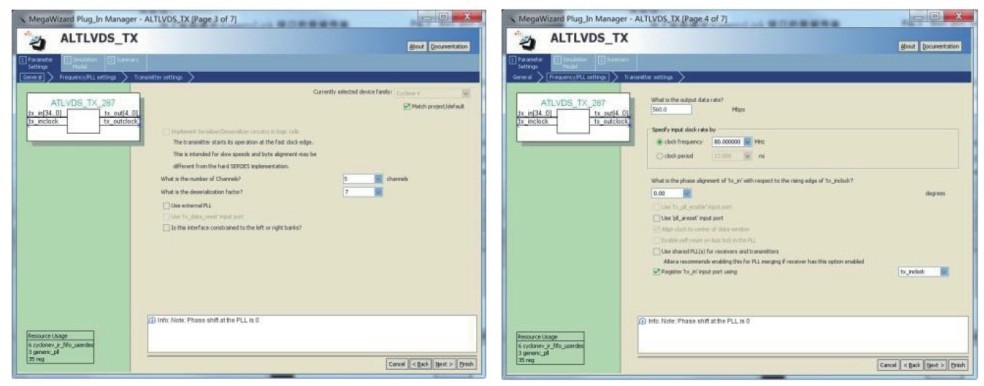

端口映射将像素点数据映射为Camera Link中抽象出的port端口,并将port端口映射为并串转换芯片的Pin-Name。根据Camera Link协议 [6] [7],抽象出端口分配图如表2所示。实际使用的CMOS探测器的输出像素为10bit数据,故本文以Camera Link的Base模式10-bit像素点为例研究。Camera Link其他像素点比如8-bit、12-bit按照协议进行类比配置即可。

表2 Base型10-bit字节的端口分配图Table 2 The port allocation diagram of Base 10-bit bytes

PortA、PortB、PortC 三 路 8-bit 信 号 和LVAL、DVAL、FVAL以及Spare信号一起构成了Camera Link图像信号的28个单端数据信号,其端口映射的Verilog代码如下:

Tx[6:0] <= {PortA[5],ortA[7],PortA[4:0]};

Tx[13:7]<={PortB[4],PortB[3],PortB[7],PortB[6], PortB[2:0]};

Tx[20:14]<={PortC[3:1],PortC[7],PortC[6],PortC[ 0],PortB[5]};

Tx[27:21]<={PortA[6],DVAL,FVAL,LVAL,Spar e,PortC[5],PortC[4]};

2.2 协议编码

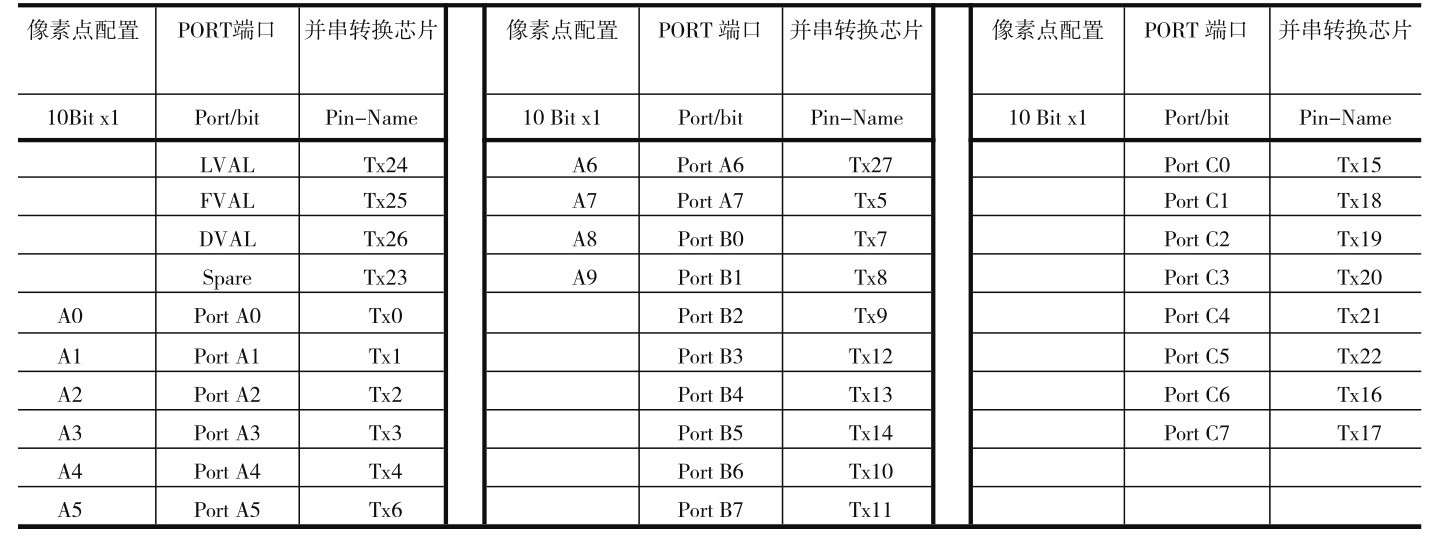

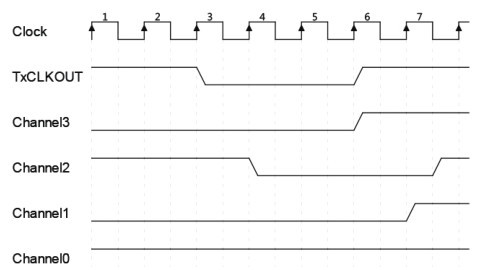

DS90CR287信号时序图如下所示 [8]

图5 DS90CR287信号时序图Fig.5 DS90CR287 signal timing diagram

将28路数据信号按照DS90CR287时序图中Pin-Name的映射位序进行编码即实现了Camera Link的数据编码功能。注意需要将同步时钟信号一起编码。协议编码的Verilog代码如下:

TxClk <= 7'b110_0011;

Chan3<={Txin[23],Txin[17],Txin[16],Txin[11],T xin[10],Txin[5],Txin[27]};

Chan2<={Txin[26],Txin[25],Txin[24],Txin[22],T xin[21],Txin[20],Txin[19]};

Chan1<={Txin[18],Txin[15],Txin[14],Txin[13],T xin[12],Txin[9],Txin[8]};

Chan0<={Txin[7],Txin[6],Txin[4],Txin[3],Txin[2] ,Txin[1],Txin[0]};

代码中Chan0-Chan3分别对应DS90CR287信号时序图中的TxOUT0-TxOUT3,表示四对LVDS数据。TxCLK对应时序图中的TxCLK OUT,表示一对LVDS时钟信号。

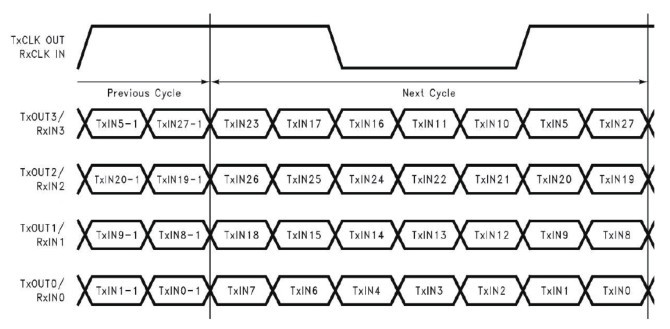

2.3 并串编码

28路数据信号与同步时钟信号编码完成后,最终通过并串编码转换,以Camera Link协议的形式输出5路LVDS信号。具体来说就是将已经编码的Chan0、Chan1、Chan2、Chan3和TxClk信号进行7:1并串转换。FPGA 内含丰富的原语和专业IP核,可实现不同的功能,并将FPGA的IO例化为多种形式的电平接口。并串转换使用的专业IP核为ALTLVDS_TX,其主要参数配置为:并行数据输入时钟80M,串行数据的输出信号速率560Mbps,使用内部锁相环PLL,用于生成所需的时钟信号,并根据PCB实际走线调试后设置合适的LVDS输出时钟相移。配置如图6。

图6 ALTLVDS_TX的IP核配置界面Fig.6 IP core configuration interface of ALTLVDS_TX

顶层例化代码如下:

ATLVDS_TX_287

ATLVDS_TX_287_inst

(.tx_in( {TxClk,Chan3,Chan2,Chan1,Chan0}),

.tx_inclock ( Clk_i ),

.tx_out ({TxCLK OUT, TxOUT3, TxOUT2, TxOUT1, TxOUT0} ),

.tx_outclock( tx_outclock_sig ));

代 码 中 TxOUT3、TxOUT2、TxOUT1、TxOUT0、TxCLK OUT表示4路LVDS数据和1路LVDS时钟,将其分配到FPGA的专用差分输出管脚,并配置为符合Camera Link标准的电气接口。

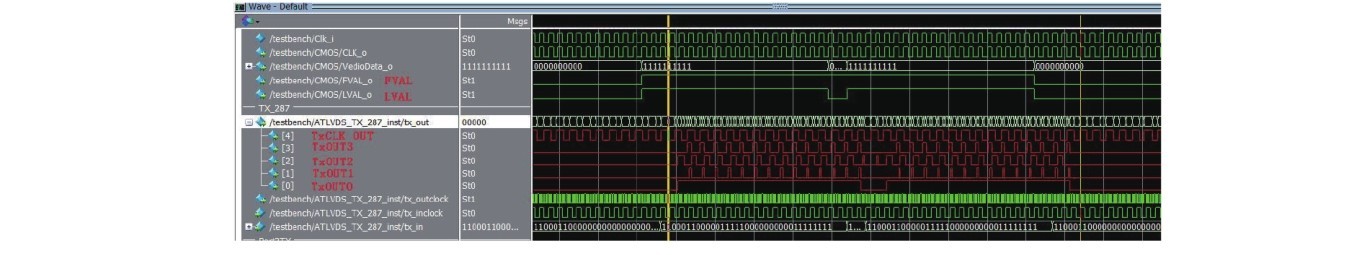

2.4 时序仿真验证

使用Modelsim SE 10.1a作为仿真平台。在Testbench中CMOS探测器输出时钟设为80M,输出的10bit数据全为1。LVAL行有效时间设置为20个像素时钟,行消隐时间设为2个像素时钟, FVAL帧有效时间设置为42个像素时钟,即每帧包括2行数据。仿真结果如下:

图7 Modelsim时序仿真图Figure.7 Modelsim timing simulation diagram

黄色线中间为一帧数据。CMOS探测器输出的一个10bit全1像素数据经并串转换模块后输出的时序图和图8一致,符合设计要求,验证了编码的正确性和可行性。

图8 时序图Fig.8 Timing diagram